fft processor chip

The input data can have arbitrary length. Successful FPGAASIC implementation of two-dimensional FFTs used in 2D image processing applications requires deep understanding of the underlying 1D FFT algorithm chip and memory architectures.

A Example Hardware Fft Implementation B Asic Processor Data Download Scientific Diagram

This paper presents a high performance FFT ASIP.

. Here is a list of some of FFTWs more interesting features 9. The full-custom design contains 460000 transistors and was fabricated in a standard single-poly triple-metal CMOS process using 07 m design rules with m. The Cooley -Tukey algorithm is a widely used FFT algorithm that exploits a divide- and-conquer approach to recursively decompose the DFT computation into smaller and smaller DFT computations until the simplest computation remains.

If we use the reduced-precision 24-bit floats in Microchip AN660 each multiply can take up to 1500 instruction cycles. Both the top-of-the-line TI device and Core2Duo see my other post on this subject today would require external memory and effective L2 cache to optimize a long FFT. With such a powerful processor its easy to sample audio and run an FFT in real time without resorting to low-level commands outside the ArduinoTeensyduino programming library.

A FFT chip with a designed throughput of 28 Gbps is implemented and fabricated to meet the requirements of above 20-Gbps throughput for wireless Gigahertz. The output of the FFT is not usually in order ie. GenFFT is the FFT code generator which produces 1D FFT kernels for various FFT lengths power of two data types cl_float and cl_half and GPU architectural details.

Navigation search A digital signal processor DSP is a specialized microprocessor designed specifically for digital signal processing generally in real-time computing. The frequency bins do not appear as bin 1 bin 2 bin 3. The implementation has already been discussed in detail in previous articles.

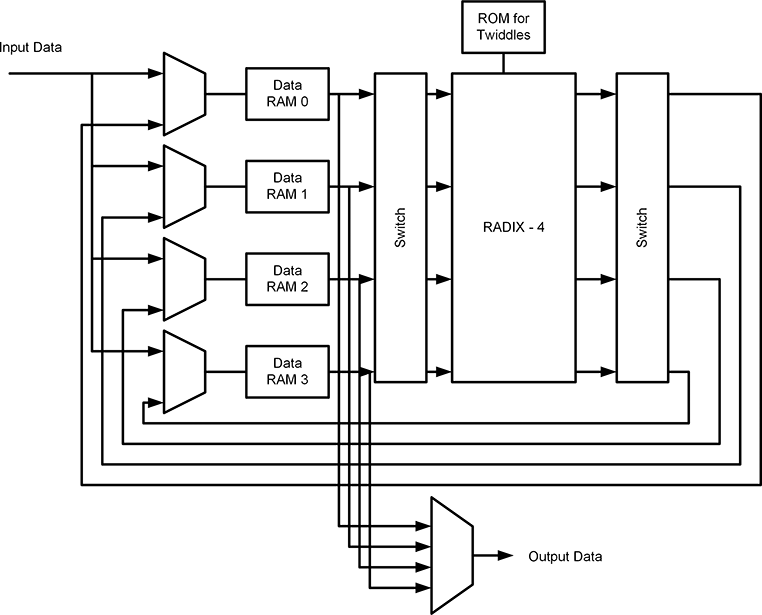

The design is based on a decimation-in-frequency radix-2 algorithm and employs in-place computation to opti-mize memory usage. Teensy 30 is a very powerful device that runs a full 32-bit ARM Cortex-M4 processor at 48 mhz. The resulting programmable solution is scalable for the order of the.

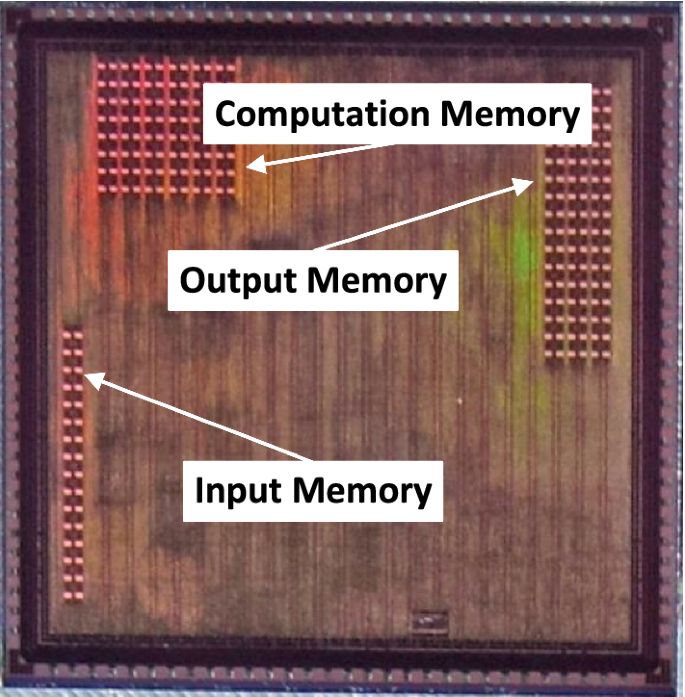

Download scientific diagram Chip microphotograph of the proposed FFT processor from publication. Since each pixel of image data is effectively processed twice. Furthermore the ARM Cortex-M4 core on the Teensy has native support for.

FFT PROCESSOR Digital signal processor From Wikipedia the free encyclopedia Jump to. In order to operate the processor data must first be loaded into the internal RAM. To address this need DSP Architectures Vancouver WA Mitel Semiconductor Kanata Ontario Canada Sharp Microelectronics Technology Camas WA Texas Memory Systems Houston TX and others.

FFTW supports fast transforms of purely real input or output data. So thats 15 million instruction cycles requiring a 60 MHz clock. Visible to Intel only GUID.

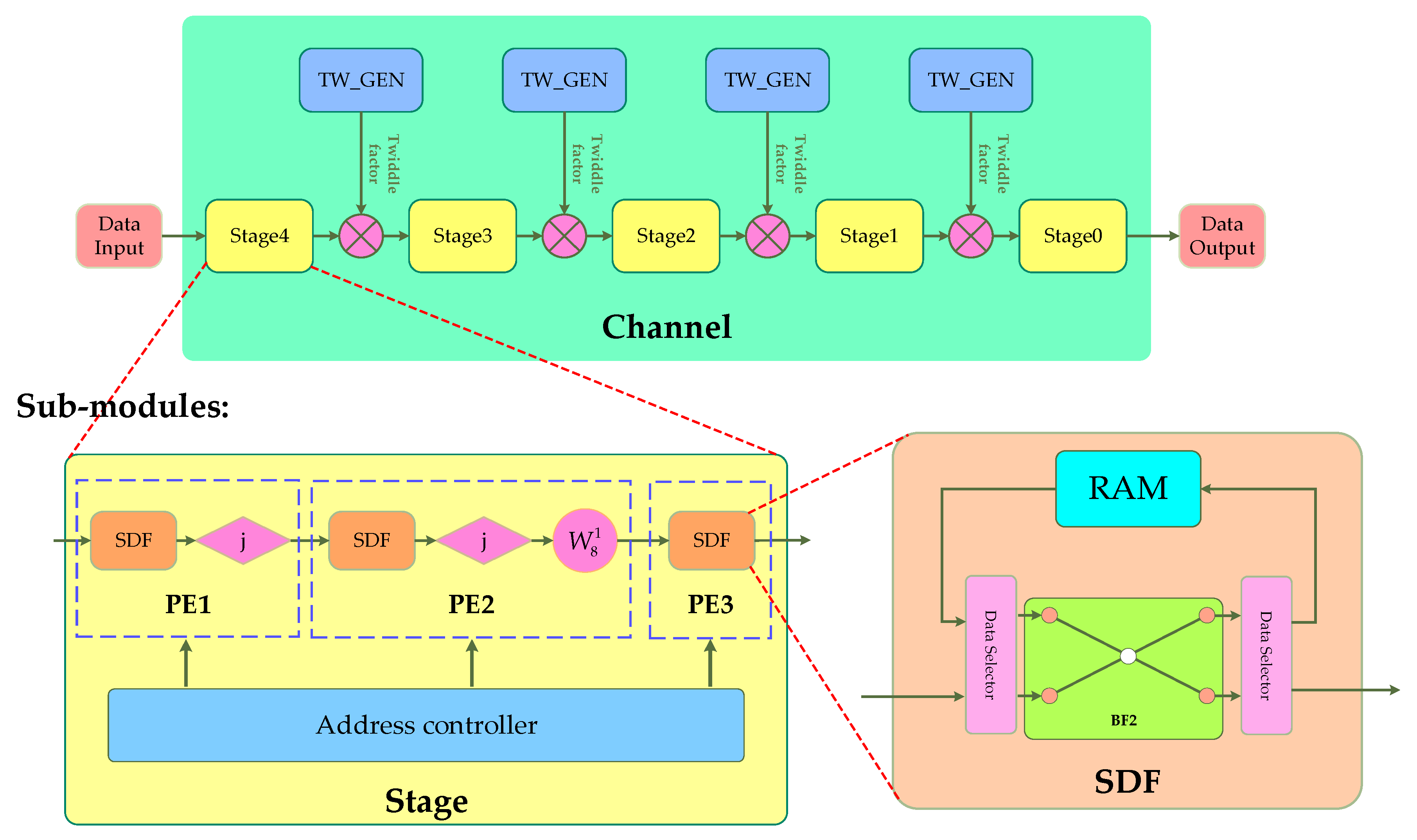

FFTW supports both one one-dimensional and multi-dimensional transforms. Performing FFT and IFFT processing is a highly computational task requiring IC architectures to be built with pipelined multiplier-accumulator stages. Document Table of Contents.

RAM equivalent of 116 x 16 at most a 32-point FFT 16-bit REAL IMAGINARY data can be implemented using on-chip RAM. Fast and efficient two-dimensional FFT core for image processing applications. The Fast Fourier Transform FFT processor is a FFT engine developed for the AT40K family of Field Programmable Gate Arrays FPGAs.

This paper presents a high performance FFT ASIP that adopts a vectorial ultra-long instruction word ULIW approach and is scalable for the order of the FFT and capable of satisfying performance requirements of various OFDM wireless standards. A high-performance photonic chipset for computing 1-D complex fast Fourier transform FFT calculations. We also designed and experimentally confirmed the operation of an SFQ-based single-chip FFT processor integrating all the component circuits.

Flip-chip integration is used to combine submicron CMOS ICs with GaAs chips containing 2-D. The PIC17C42 has instructions TABLRD TABLWT to transfer data between program memory space and on-chip file registers. A 1024-point single-chip FFT processor namedSpiffee was designed and fabricated.

DSP chip often have memory dedicated to storing the FFT twiddle factors ie. INTRODUCTION The Fast Fourier transform FFT and its inverse 1FET is one of the fundamen- tal operations in. FFTW employs O n log n algorithms for all lengths including prime numbers.

A 64k FFT brings other factors into the equation. A Low-Memory-Access Length-Adaptive Architecture for 2 n n -Point FFT. PMOS thresholds are 930 mV and NMOS thresholds are 680 mV.

Well a 64k FFT in 250 usec is asking a lot. Document Table of Contents. In addition the DSP needs to do at least 4 of these streams simultaneously.

View More See Less. The FFT processor which is implemented in a standard 035 pm CMOS process is efficient in term of power consumption and chip area. To compute higher point FFTs the data can be stored in the program memory space of the PIC17C42.

The sin and cos factors. In this study to complete the FFT processor design we designed and demonstrated residual component circuits called a rounding circuit and a data buffer at a target frequency of 50 GHz. The sample project shows one way of using genFFT to generate and enqueue FFT kernels in your application.

The processor occupies 5985. Contents hide 1 Typical characteristics 2 Architectural features 21 Program flow. You need to do about 10000 multiplies to run FFT on a 1024-point sample.

The FFT is a class of efficient DFT implementations that produce results identical to the DFT in far fewer cycles. On GPUs these factors can be stored in the cache but it is usually not explicit and can not be guaranteed. This FFT chip is the fastest and the most efficient for wireless LANs.

Vlsi Design Of Low Cost And High Precision Fixed Point Reconfigurable Fft Processors Xiao 2018 Iet Computers Amp Digital Techniques Wiley Online Library

This Is A Sbc Calls Z Turn Board The Center Processor Is Xc7z010 020 Dual Core Arm Cortex A9 Processor From Xilinx Turn Ons Microcontrollers Linux

A High Flexible Low Latency Memory Based Fft Processor For 4g Wlan And Future 5g Semantic Scholar

The Proposed Variable Length Fft Ifft Processor Architecture Download Scientific Diagram

Dft With Fft Algorithm Using Tms320c67xx Dsp Processor Youtube

A 28 Gbps Radix 16 512 Point Fft Processor Based Continuous Streaming Ofdm For Wigig Springerlink

High Resolution Single Chip Radix Ii Fft Processor For High Tech Application Intechopen

Electronics Free Full Text An Fpga Based Four Channel 128k Point Fft Processor Suitable For Spaceborne Sar Html

The Basic Architecture Of The Fft Ifft Processor Download Scientific Diagram

Tms320c5517 Fixed Point Digital Signal Processor Ti Mouser

High Resolution Single Chip Radix Ii Fft Processor For High Tech Application Intechopen

1 Tabular Comparison Of Fft Processor Performance Download Table

A Example Hardware Fft Implementation B Asic Processor Data Download Scientific Diagram

A Prototype Analog Mixed Signal Fast Fourier Transform Processor Ic For Ofdm Receivers Semantic Scholar

A Prototype Analog Mixed Signal Fast Fourier Transform Processor Ic For Ofdm Receivers Semantic Scholar

High Resolution Single Chip Radix Ii Fft Processor For High Tech Application Intechopen

0 Response to "fft processor chip"

Post a Comment